ムーアの法則が限界へ、突破口は「積層」

今や私たちの生活に欠かせないスマートフォンやパソコンの性能は、「トランジスタ」という微細な電子部品がいくつ搭載されているかで大きく決まります。

そのトランジスタの数を「約2年ごとに倍増できる」という夢のような法則が、半導体業界に長年君臨してきた「ムーアの法則」です。

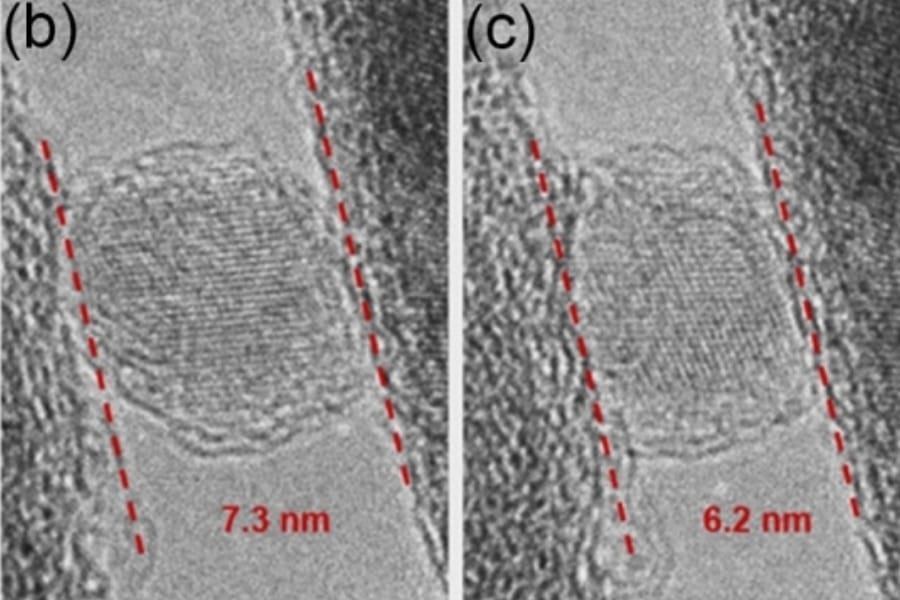

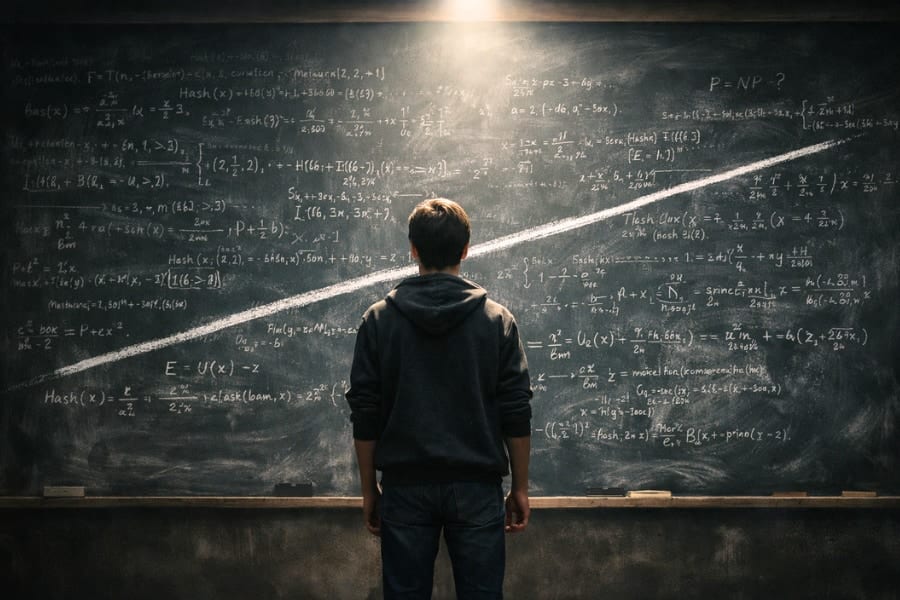

しかし、近年、この「トランジスタをどんどん小さくする」道のりが物理的な限界に近づいてきました。

なぜかというと、トランジスタをあまりにも小さくしすぎると、今まで問題にならなかった量子トンネル効果という現象によって電流が漏れてしまうからです。

これは、本来電気が流れてはいけない場所に電流が勝手に通り抜ける現象で、せっかく細かなトランジスタを作っても性能が下がってしまうのです。

さらに、小型化が進むほど製造装置や手順が極端に複雑になり、コストも急激に高騰するという悪循環が起きています。

つまり、ただ平面的にトランジスタを小さくしていく道だけでは、性能向上が頭打ちになってしまうのです。

こうした問題を背景に、「小型化の限界に近づいた今、これからは平面以外の方向にも目を向けなければならない」という意識が業界全体で高まっています。

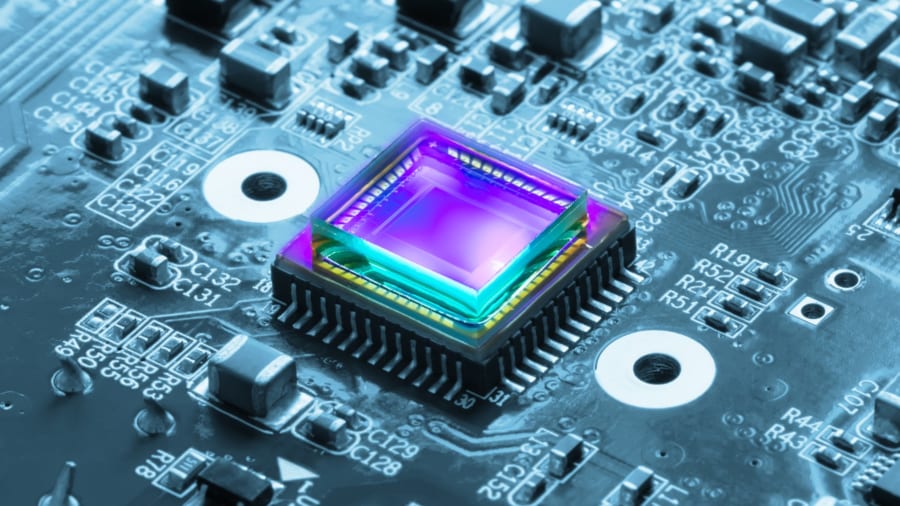

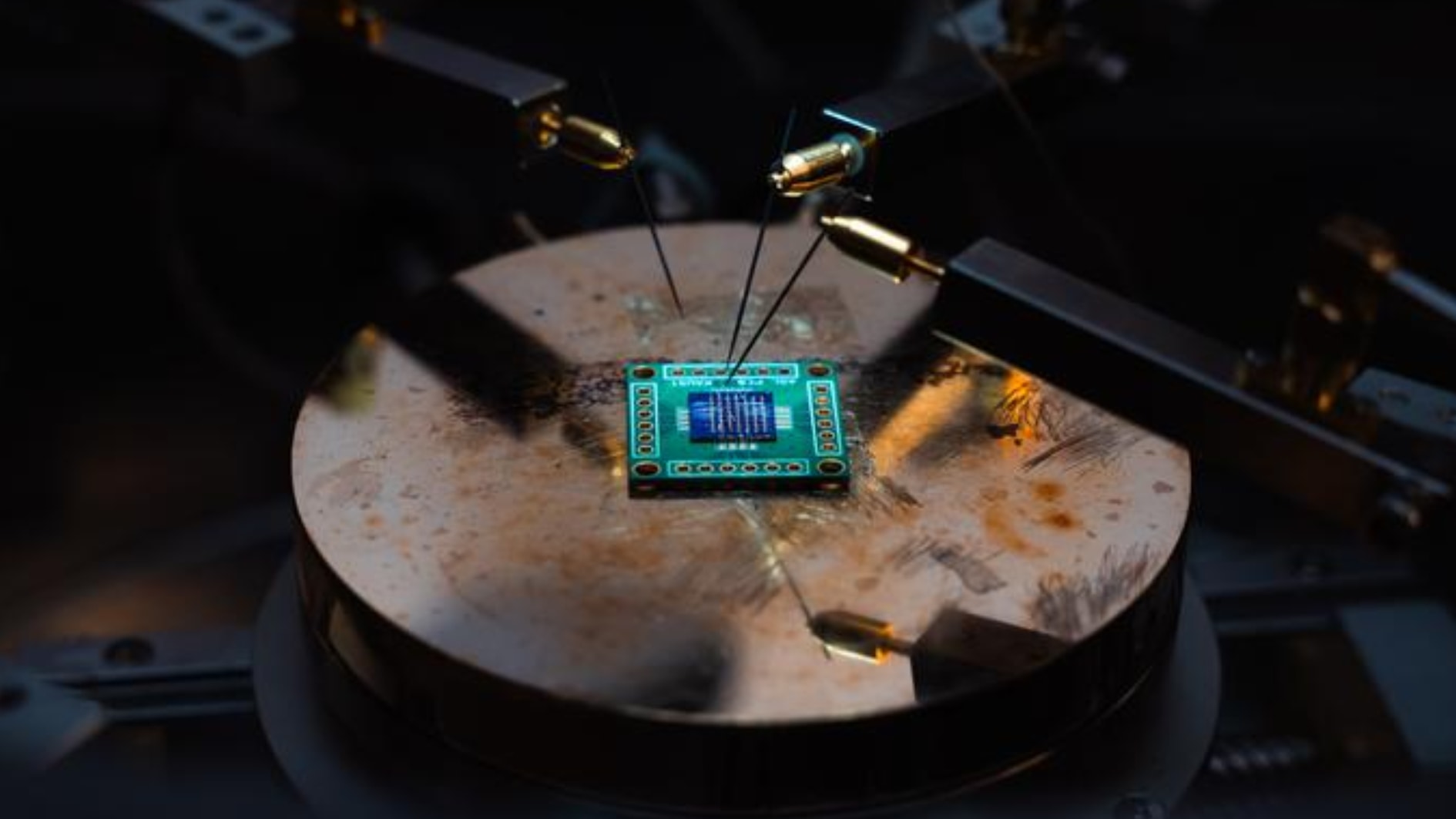

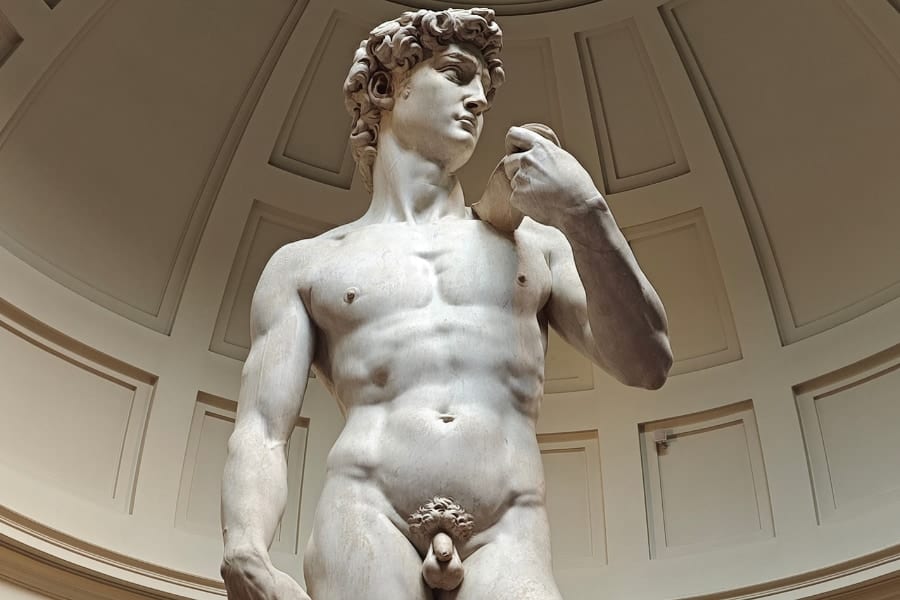

そこで注目されているのが、チップを平面的にではなく縦方向に重ねて積むという新しいアプローチです。

とくに期待されているのが、有機素材と無機素材という異なるタイプの半導体を組み合わせて作るハイブリッドCMOSチップです。

従来の半導体チップは、主にシリコン(ケイ素)という無機材料だけを使って作られてきましたが、ハイブリッドCMOSチップは、シリコンなどの無機材料に、有機材料(プラスチックに近い高性能樹脂)を組み合わせて作るのが特徴です。

この異なる材料の組み合わせは、比較的低い温度で製造できるという利点があり、高温に弱い柔軟な基板や大きな面積の基板でも作りやすいと期待されています。

これにより、従来のシリコンチップでは難しかった、折り曲げ可能な電子回路や身体に貼りつけられるウェアラブルデバイスの実現にも道が開ける可能性があります。

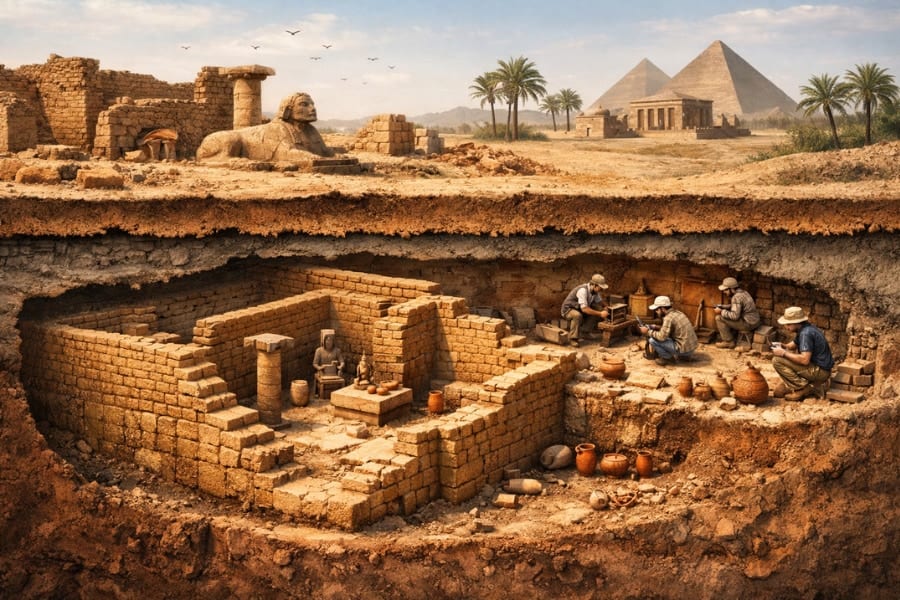

ただし、この縦に積む「3次元集積化」という手法には、まだ大きな課題が残っています。

有機材料と無機材料では、製造温度や加工方法が異なるため、交互に積み重ねる際にうまく適合させるのが難しいのです。

異なる材料を使った層を重ねていくと、接合面がデコボコになったり、熱によるダメージや層同士のズレが蓄積したりする問題が発生します。

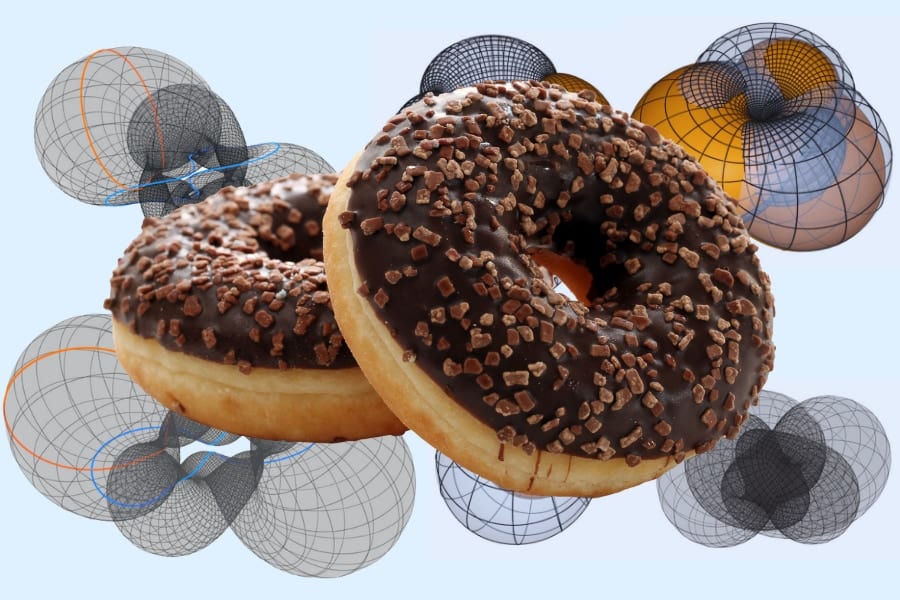

いわば、異なる材料でできた繊細な層を何段にも重ねる「多層ケーキ」を作るようなもので、一段ごとの精度が少しでも狂うと全体の出来栄えに影響してしまうのです。

そのため、これまではハイブリッドCMOSの積層構造は実用上せいぜい2段が限界で、それ以上の多層化は難しいとされてきました。

では、もしこの技術的な壁を突破してチップを3段、4段、さらには6段以上も積み重ねることができたら、何が起きるのでしょうか。

横方向の小型化に頼らず、縦方向にトランジスタの数を増やせるとすれば——

それはムーアの法則の限界を超える、新しい進化の道になるかもしれません。

![よーく聞いてね!3つのヒントで学ぶ!どうぶつカード ([バラエティ])](https://m.media-amazon.com/images/I/51zT3OcliFL._SL500_.jpg)

![シルバーバック かわいい海の生きもの CUBE 2X2 キューブ ツーバイツー|海の生き物デザイン 立体パズル スピードキューブ 5cm 子ども〜大人向け 知育 ギフトに最適 ([バラエティ])](https://m.media-amazon.com/images/I/41EJOOLgGXL._SL500_.jpg)