立体積層チップはいかにして成功したか

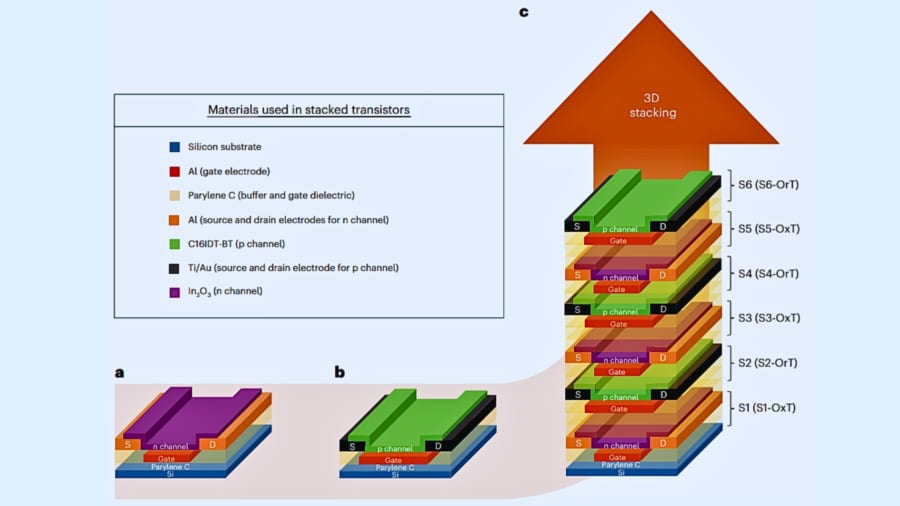

研究チームは挑戦にあたり、無機と有機という性質のまったく違う2種類の半導体に注目しました。

n型の金属酸化物トランジスタ(電子が動くタイプ)には酸化インジウム(In₂O₃)という無機材料を、p型の有機半導体トランジスタ(正孔が動くタイプ)にはC16IDT-BTという樹脂系の高性能材料を使いました。

この異なる材料を交互に積み重ねることで、ひとつのチップの中に“2つの世界”を共存させることができるのです。

有機はやわらかくて加工しやすく、無機は硬くて丈夫。両者の長所をうまく組み合わせることが狙いでした。

ただし、これを6段も重ねるのは並大抵のことではありません。

最大の敵は「熱」でした。

高温の製造工程を使えば下の層の有機物が焦げてしまう一方、温度を下げすぎると層をしっかり固めることができません。

この難題を解くために研究チームは、製造の多くを室温近くで行い、主要な工程を150℃以下に抑える工夫をしました。

さらに、200℃で短時間の加熱処理を行うことで、トランジスタの開閉特性(SS値)を改善できることもわかりました。

つまり、「焦がさず固める」というギリギリの温度設定を見つけ出したのです。

もちろん、積み重ねにはもうひとつの壁――“ズレ”の問題もありました。

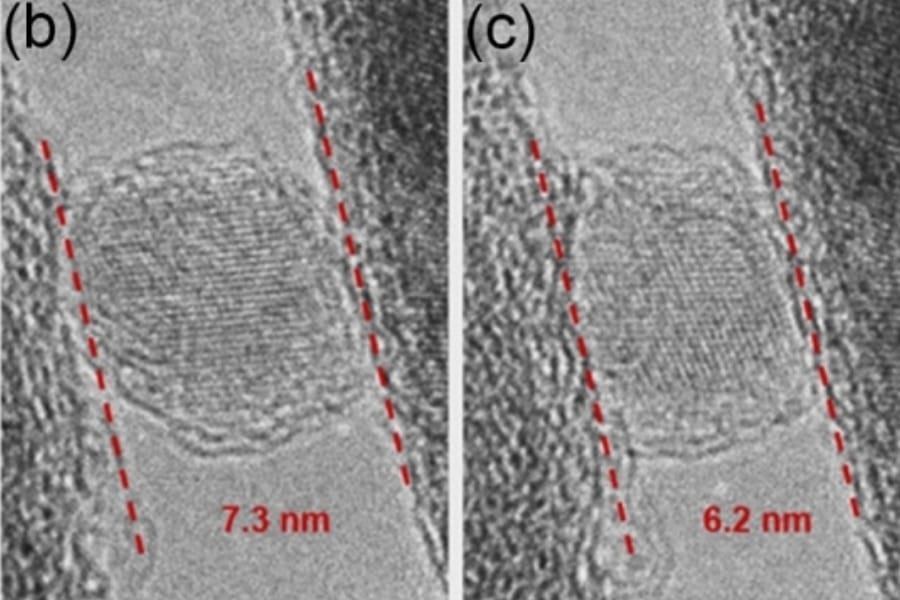

層の表面がわずかに波打つだけでも、上に乗せた層がうまく動かなくなるのです。

研究チームは、各層の表面をナノメートル単位で磨き上げ、層と層の位置を正確に合わせる技術を磨き上げました。

結果として、6層をきれいに積み上げた“電子のタワー”が完成しました。

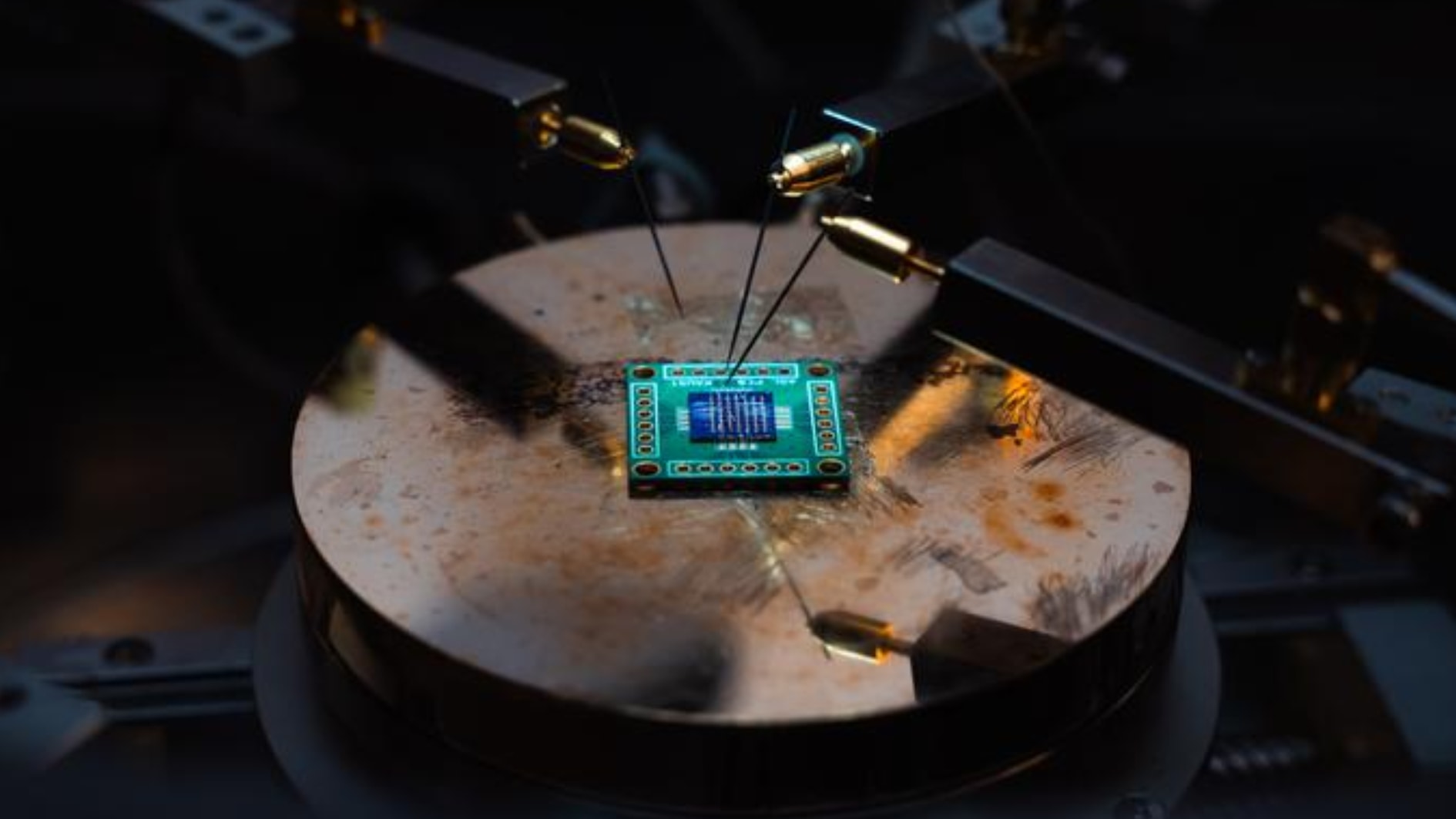

実際の評価では、測定用の細い針のような電極を使って各層の電気的な性能を調べました。

すると、6層のトランジスタはいずれもおおむね設計どおりに動作し、積層による性能の劣化はわずかであることが確認されました。

下の層ほど安定しており、上に行くほどややばらつきが出ましたが、全体としては良好な結果でした。

この段階で、彼らが積み上げた構造が単なる実験ではなく、実用化に近い設計になりつつあることがわかりました。

そのうえで、チームは600個のトランジスタを使って300個のインバータ回路(入力信号を反転させる基本ユニット)を作成し、その動作を詳しく調べました。

結果は驚くべきもので、6層チップのインバータは入力電圧の約94.84倍を出力に変換できる高い増幅率(ゲイン)を示しました。

しかも消費電力はわずか0.47マイクロワット。

従来の報告では、同じ規模のインバータ回路に約210マイクロワットが必要でした。

比較すると、今回のチップはおよそ450分の1という圧倒的な省エネ性能を実現したことになります。

電気をほとんど使わずに信号を増幅できる――これはまさに「静かに力強いチップ」と言えるでしょう。

この成果の裏には、トランジスタを縦に積み重ねることで配線距離を短くし、電流の流れを効率的にした効果があります。

つまり、“横に広げる”のではなく“上に伸ばす”ことで、チップ全体のエネルギー損失を大きく抑えたのです。

その結果、性能と省エネという、これまで両立が難しかった目標を同時に実現することに成功しました。

この新しいアプローチは、単なる性能アップにとどまりません。

たとえば、曲げられるディスプレイや体に貼るセンサーなど、薄くて広い電子デバイスの内部で、より高密度な頭脳を作る鍵になる可能性があります。

平面の限界を立体的な積層で突破しようというこの試み――その第一歩が、今回の6段チップなのです。

![よーく聞いてね!3つのヒントで学ぶ!どうぶつカード ([バラエティ])](https://m.media-amazon.com/images/I/51zT3OcliFL._SL500_.jpg)

![シルバーバック かわいい海の生きもの CUBE 2X2 キューブ ツーバイツー|海の生き物デザイン 立体パズル スピードキューブ 5cm 子ども〜大人向け 知育 ギフトに最適 ([バラエティ])](https://m.media-amazon.com/images/I/41EJOOLgGXL._SL500_.jpg)